Quick Note: Intel “Knights Landing” Xeon Phi & Omni-Path 100 @ ISC 2015

by Ryan Smith on July 13, 2015 6:30 PM EST

Taking place this week in Frankfurt, Germany is the 2015 International Supercomputing Conference. One of the two major supercomputing conferences of the year, ISC tends to be the venue of choice for major high performance computing announcements for the second half of the year and is where the summer Top 500 supercomputer list is unveiled.

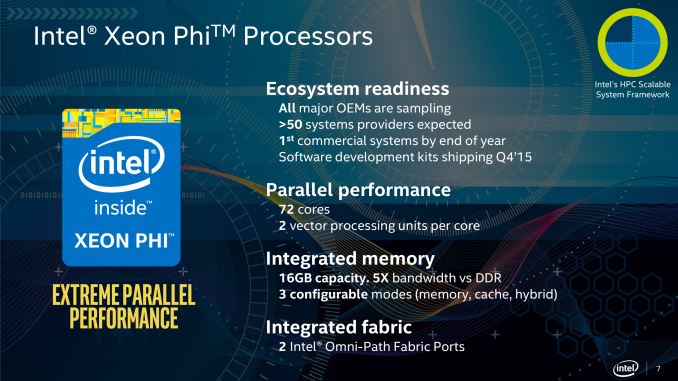

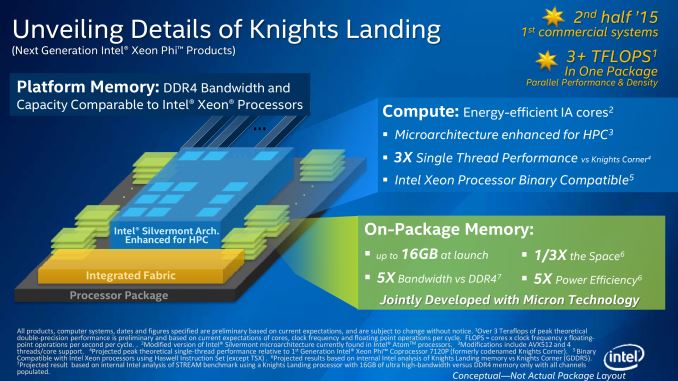

In any case, Intel sends word over that they are at ISC 2015 showing off the “Knights Landing” Xeon Phi, which is ramping up for commercial deployment later this year. Intel unveiled a number of details about Knights Landing at last year’s ISC, where it was announced that the second-generation Xeon Phi would be based on Intel’s Silvermont cores (replacing the P54C cores in Knights Corner) and built on Intel’s 14nm process. Furthermore Knights Landing would also include up to 16GB of on-chip Multi-Channel DRAM (MCDRAM), an ultra-wide stacked memory standard based around Hybrid Memory Cube.

Having already revealed the major architecture details in the last year, at this year’s show Intel is confirming that Knights Landing remains on schedule for its commercial launch later this year. This interestingly enough will make Knights Landing the second processor to ship this year with an ultra-wide stacked memory technology, after AMD’s Fiji GPU, indicating how quickly the technology is being adopted by processor manufacturers. More importantly for Intel of course, this will be the first such product to be targeted specifically at HPC applications.

Meanwhile after having previously announced that the design would include up to 72 cores - but not committing at the time to shipping a full 72 core part due to potential yield issues - Intel is now confirming that one or more 72 core SKUs will be available. This indicates that Knights Landing is yielding well enough to ship fully enabled, something the current Knights Corner never achieved (only shipping with up to 61 of 62 cores enabled). Notably this also narrows down the expected clockspeeds for the top Knights Landing SKU; with 72 cores capable of processing 32 FP64 FLOPs/core (thanks to 2 AVX-512 vector units per core), Intel needs to hit 1.3GHz to reach their 3 TFLOPs projection.

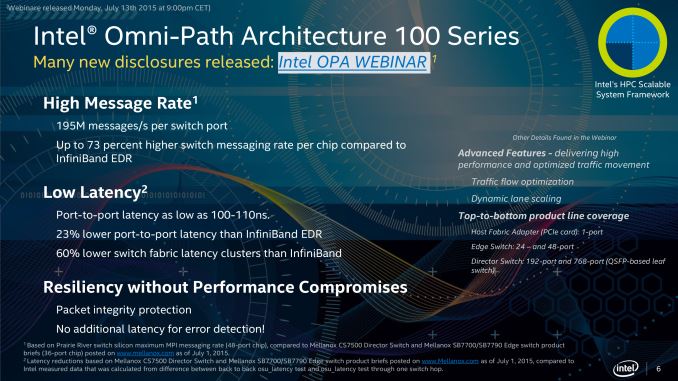

Moving on, Knights Landing’s partner interconnect technology, Omni-Path, is also ramping up for commercial deployment. After going through a few naming variants, Intel has settled on the Omni-Path Fabric 100 series, to distinguish it from planned future iterations of the technology. We won’t spend too much on this, but it goes without saying that Intel is looking to move to a vertically integrated ecosystem and capture the slice of HPC revenue currently spent on networking with Infiniband and other solutions.

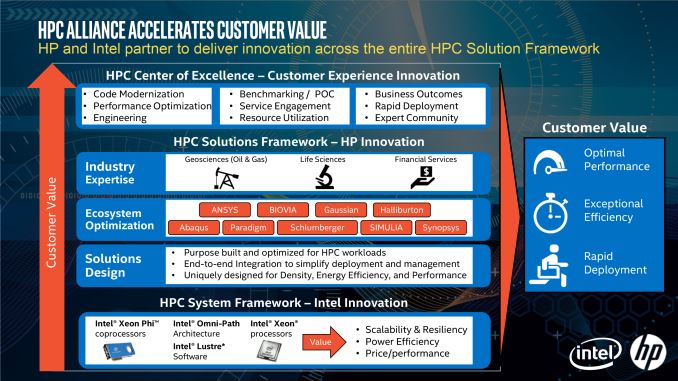

Finally, in order to develop that vertically integrated ecosystem, Intel is announcing that they have teamed up with HP to build servers around Intel’s suite of HPC technologies (or as Intel calls it, their Scalable System Framework). HP will be releasing a series of systems under the company’s Apollo brand of HPC servers that will integrate Knights Landing, Omni-Path 100, and Intel’s software stack. For Intel the Apollo HPC systems serve two purposes: to demonstrate the capabilities of their ecosystem and the value of their first-generation networking fabric, and of course to get complete systems on the market and into the hands of HPC customers.

Source: Intel

53 Comments

View All Comments

mdriftmeyer - Monday, July 13, 2015 - link

HBM 2.0 GPGPUs for AMD FirePro and Nvidia will make this platform far less compelling.SaberKOG91 - Monday, July 13, 2015 - link

Especially considering the barrier to entry. With AMD you have OpenCL and Nvidia has CUDA/OpenCL. These Phi cards are closer to complete systems than coprocessors. Programming for them is non-trivial and requires a lot of sifting through documentation.beginner99 - Tuesday, July 14, 2015 - link

No, not anymore. As the slide states and has been known for a while Knight Landing is binary compatible to Haswell (except for TSX instructions). Makes sense because after all these are Silvermont (Atom) cores with some added FP64 punch. That's also why it is available as socketed variant. this thing can run Windows/Linux and any other x86 code your current Xeon is running.It's exactly the opposite to what you claimed. Barrier for entry is much lower with this new Xeon Phi.

coolbho3k - Tuesday, July 14, 2015 - link

>Knight Landing is binary compatible to Haswell (except for TSX instructions)Haswell supports TSX instructions now? News to me. ;)

close - Tuesday, July 14, 2015 - link

"Intel is announcing that they have teamed up with HP"Whenever I see Intel teaming up with HP I think Itanium :).

Refuge - Tuesday, July 14, 2015 - link

Haha, I had the exact same thought when I read that. :PSamus - Tuesday, July 14, 2015 - link

Itanium IA64 wasn't bad technology, but where Intel screwed up was pressuring HP to push it into the consumer space where it never belonged. AMD knew, and executed on, a x86-compatible 64-bit instruction set for consumer applications.So by binary compatible, is the Phi x86-based or does it emulate x86? I assumed ditching P54c indicates they ditched x86 but I'm not familiar with Silvermonts architecture? Does it just emulate x86 instructions?

LukaP - Tuesday, July 14, 2015 - link

Silvermont is a native x86-64 architecture. :) Its used in Atom CPUs and with the extra SIMD units, in KLs :)68k - Tuesday, July 14, 2015 - link

Haswell based Xeon E7 do support TSXhttp://techreport.com/news/28225/xeon-e7-v3-boasts...

It is however broken on consumer products, and according to the TR-article, also broken on Haswell based Xeon E5.

Refuge - Friday, July 17, 2015 - link

As far as I know it has always been supported by Haswell chips.