Estimating Intel-Micron 32-layer 3D NAND Die Size

by Kristian Vättö on March 27, 2015 5:55 AM EST

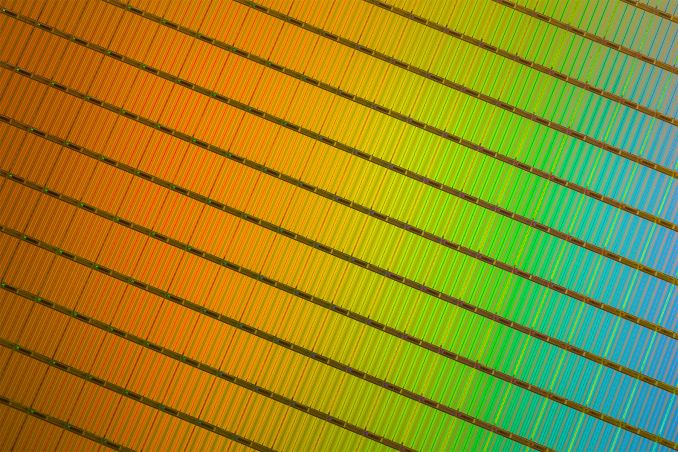

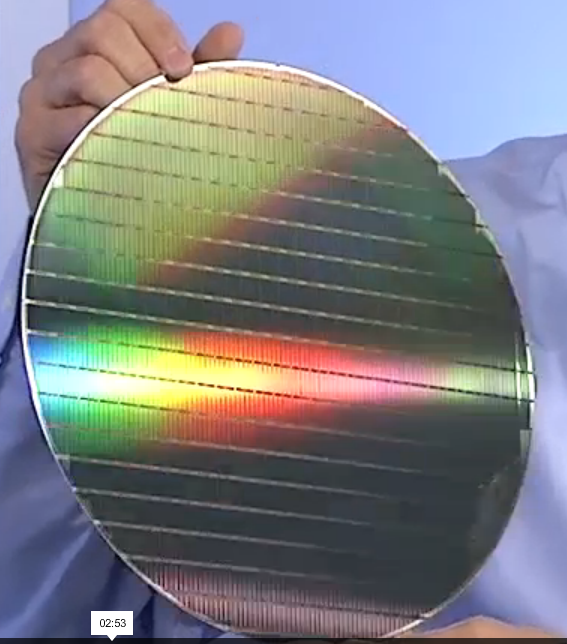

Yesterday Intel and Micron shared some new details of their 3D NAND technology and during the presentation they also showed a production wafer. I missed the wafer during the live broadcast (hence I couldn't include this in the initial write up), but fortunately Intel-Micron have now posted the recorded webinar, which I used to get a pretty good shot of the wafer. The quality isn't perfect, but it's good enough that I was able to make a fairly accurate estimation of the die size.

Disclaimer: The data and analysis presented in this article is based on estimations that are provided "as is" with no guarantee of full accuracy.

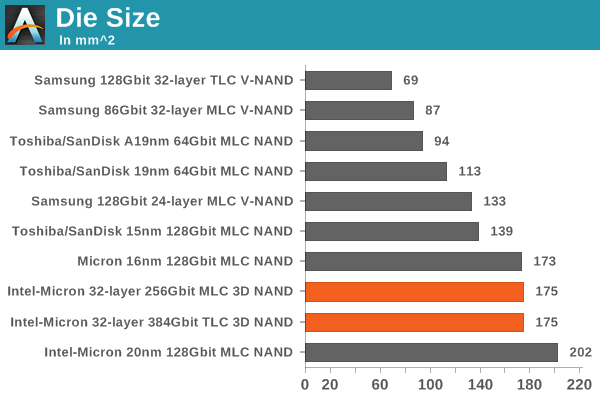

I calculated 19 dies vertically and 25 horizontally, which would yield a die size of 189.5mm. That's a bit too high since it doesn't take the partial dies on the edges of the wafer into account, so when taking that and the die cuttings (i.e. the space between dies) into account, my estimation of the die size would be 175mm. I think in reality it might be closer to 170mm, but I'll rather be conservative than present too optimistic numbers.

My die size estimation goes pretty well hand-in-hand with Intel-Micron's planar NAND dies. The two have never really focused on building small dies for mobile applications (e.g. microSD cards), which is why the die sizes are higher compared to the others with mobile focus. I was told Intel-Micron might build a smaller two-plane 3D NAND for mobile use if they see demand for it, but as I mentioned in yesterday's news post the initial die will be a 4-plane design that is aimed for SSDs.

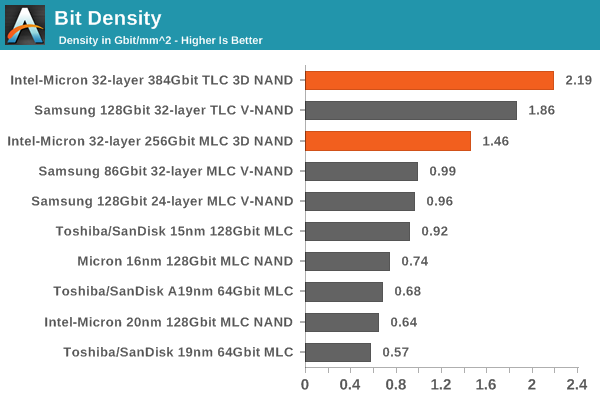

Now that we have the die size we can also estimate the most important metric i.e. the bit density. Intel-Micron's 32-layer 3D NAND design is by far more efficient than Samsung's, which is mostly explained by the much higher die capacity. The memory array efficiency (i.e. the portion of the die that's dedicated to memory cells) tends to scale with die capacity because the peripheral circuitry doesn't need too many modifications and thus the die area taken by the circuitry doesn't really increase with capacity.

I estimated Intel-Micron's 32-layer 3D NAND to have array efficiency of approximately 85%, which is very good and considerably higher than Samsung's 32-layer design (66% for the 86Gbit MLC part and 72% for the 128Gbit TLC part). Samsung did some peripheral circuitry optimizations for the 32-layer TLC part that explain the higher array efficiency versus the MLC part. When assuming similar array efficiencies for Intel-Micron and Samsung TLC dies, the bit densities are actually equivalent, suggesting that from a lithography and cell size perspective the two designs should be quite similar.

I now understand why Intel-Micron claim that their 3D NAND technology comes with disruptive cost because it really is the most efficient 3D NAND technology we have seen so far. It has twice the bit density compared to Micron's latest 16nm 128Gbit die, which should be enough to mitigate the higher production cost per wafer and make 3D NAND a natural successor to Intel-Micron's planar NAND. It will be interesting to see how Samsung's third generation V-NAND stacks up against Intel-Micron's 32-layer 3D NAND, but it's clear that Samsung must be able to increase the die capacity to remain competitive as it's more than just a game of layers.

36 Comments

View All Comments

CristianM - Friday, March 27, 2015 - link

I am sure that these chips have more or less redundancy built in. The first iterations from Samsung might have had a lot more than the latest tlc models. the final cost of the product is greatly influenced by yields. So a bigger die that has more redundancy built in that yields more might be cheaper than a smaller die.The big advantage that I see for Samsung is that they have far more experience with the process and they will continue to fine tune it.

I hope that everyone will find their way and prices will fall.

nandnandnand - Friday, March 27, 2015 - link

Where is Toshiba's 48 layer NAND?psychobriggsy - Friday, March 27, 2015 - link

The die size isn't known. However if you extrapolate Samsung's density to 48 layers you can see it will be very competitive. This will be coming this year.melgross - Friday, March 27, 2015 - link

Next year.eddieobscurant - Friday, March 27, 2015 - link

nope , toshiba's 48 layer nand, won't be coming into consumer products before q2/2016Shadowmaster625 - Friday, March 27, 2015 - link

So in the year 2015, we can now fit the entire library on congress on a 62 sq inch piece of silicon?RU482 - Friday, March 27, 2015 - link

impress me and figure out how many times you can fill the library of congress with 62 sq inch pieces of siliconMr Perfect - Saturday, March 28, 2015 - link

Time to email Randall at XKCD.jjj - Friday, March 27, 2015 - link

Toshiba/Sandisk do have 50% more layers so they are likely more efficient even with half the capacity.To be fair die size is less relevant now when the number of layers and the technology differs.

Kristian Vättö - Friday, March 27, 2015 - link

I agree with both of you points. I would honestly be surprised if Toshiba-SanDisk's 48-layer isn't more efficient, especially since it will enter the market later. I think die size and bit density are still important metrics when comparing different dies, but you're right that it's no longer possible to use die size as the sole indicator of cost efficiency because there are so dramatic differences in the structures and manufacturing processes.