One More EPYC: AMD Launches Entry-Level Zen 4-based EPYC 4004 Series

by Ryan Smith on May 21, 2024 9:00 AM EST- Posted in

- CPUs

- AMD

- Enterprise CPUs

- EPYC

- Zen 4

- Raphael

- 3D V-Cache

- EPYC 4004

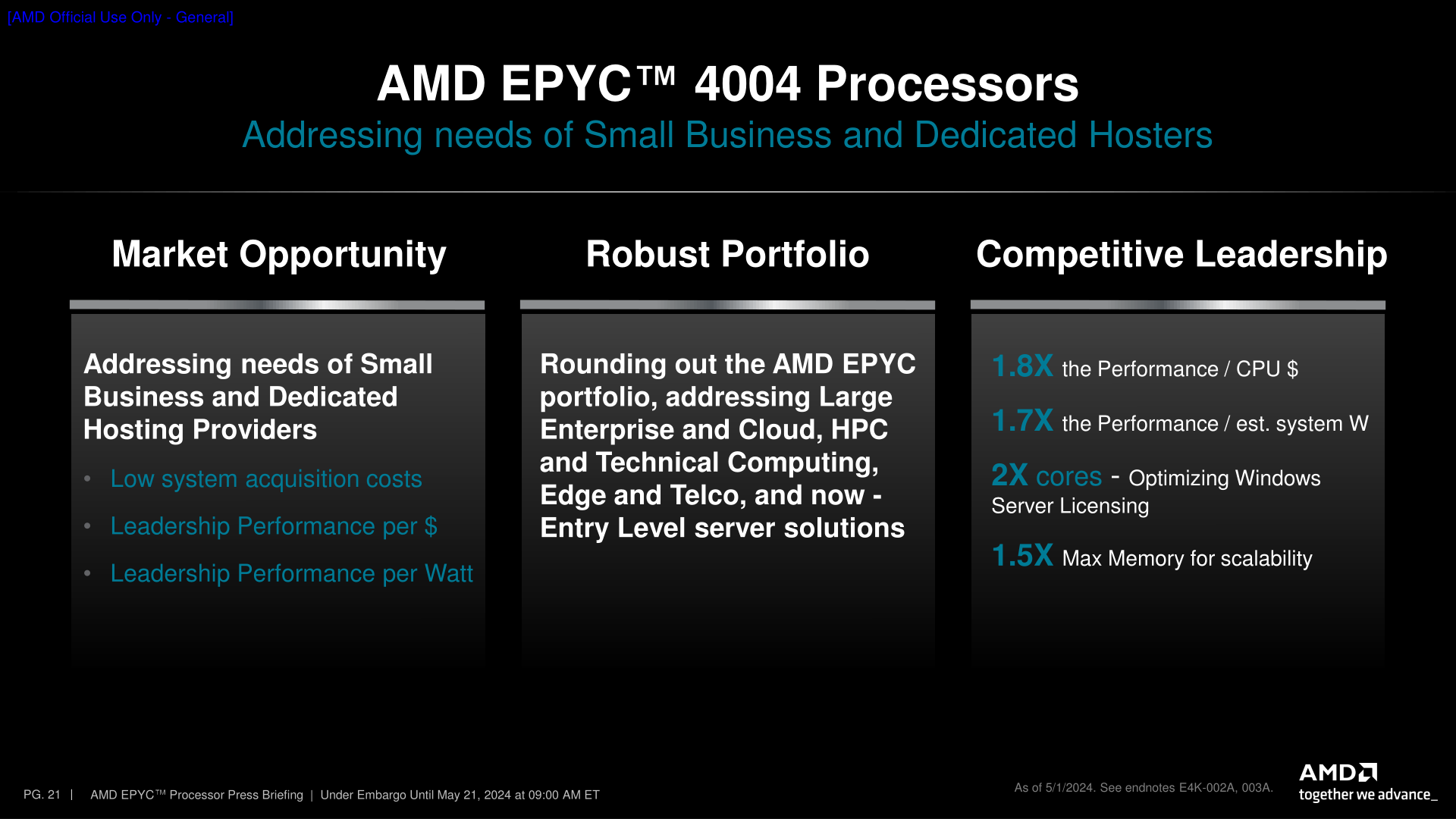

Ever since AMD re-emerged as a major competitor within the x86 CPU scene, one of AMD’s top priorities has been to win over customers in the highly lucrative and profitable server market. It’s a strategy that’s paid off well for AMD, as while they’re still the minority player in the space, they’ve continued to whittle away at what was once Intel’s absolute control over the market, slowly converting more and more customers over to the EPYC ecosystem.

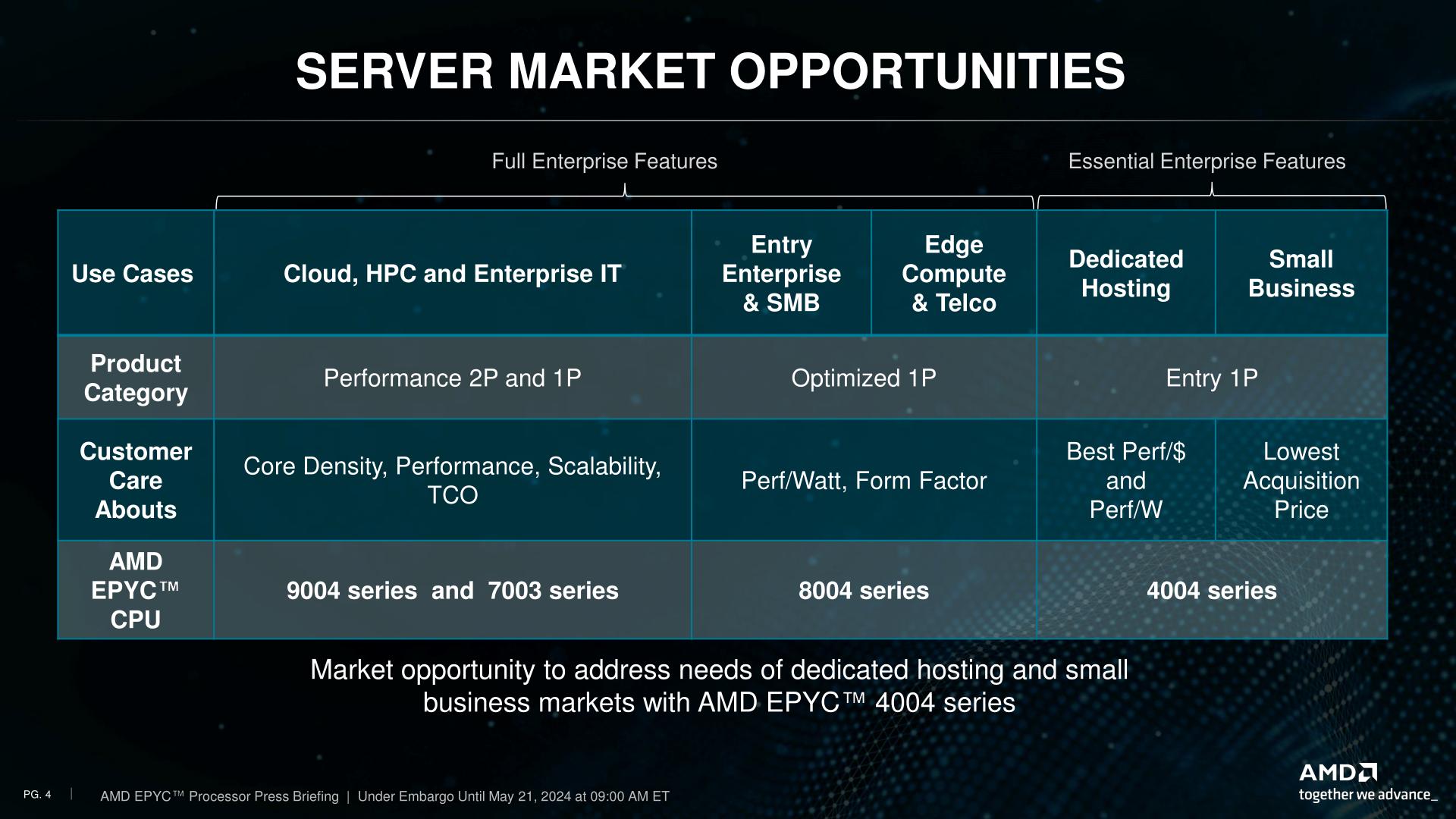

Now as the Zen 4 CPU architecture approaches its second birthday, AMD is launching one final line of EPYC chips, taking aim at yet another Xeon market segment. This time it’s all about the entry-level 1P server market – small scale, budget-conscientious users who only need a handful of CPU cores – which AMD is addressing with their new EPYC 4004 series processors.

Within AMD’s various product stacks, the new EPYC 4004 family essentially replaces Ryzen chips for use in servers. Ryzen for servers was never a dedicated product lineup within AMD, but none the less it has been a product segment within the company since 2019, with AMD aiming it at smaller-scale hosting providers who opted to use racks of consumer-scale hardware, rather than going the high-density route with high core count EPYC processors.

With the upgrade to EPYC status, that hardware ecosystem is being re-deployed as a proper lineup with dedicated chips, and a handful of additional features befitting an EPYC chip. Consequently, AMD is also expanding the scope of the market segments they’re targeting by a hair, roping in small business (SMB) users, whom AMD wasn’t previously chasing. Though regardless of the name on the market segment, the end result is that AMD is carving out a budget-priced series of EPYC chips with 4 to 16 cores based on their consumer platforms.

Underlying the new EPYC 4004 series is AMD’s tried and true AM5 platform and Raphael processors, which we know better as the Ryzen 7000 series. Their new EPYC counterparts are an 8 chip stack that is comprised almost entirely of rebranded Ryzen 7000 SKUs, with all the same core counts, clockspeeds, and TDPs as their counterparts. The sole exception here being the very cheapest chip of the bunch, the 4 core 4124P.

| AMD EPYC 4004 Processors | ||||||||||

| AnandTech | Core/ Thread |

Base Freq |

1T Freq |

L3 Cache |

PCIe | Memory | TDP (W) |

Price (1KU) |

Ryzen Version | |

| 4584PX | 16 | 32 | 4200 | 5700 | 128MB (3D) | 28 x 5.0 | 2 x DDR5-5200 UDIMM | 120 | $699 | 7950X3D |

| 4484PX | 12 | 24 | 4400 | 5600 | 128MB (3D) | 120 | $599 | 7900X3D | ||

| 4564P | 16 | 32 | 4500 | 5700 | 64MB | 170 | $699 | 7950X | ||

| 4464P | 12 | 24 | 3700 | 5400 | 64MB | 65 | $429 | 7900 | ||

| 4364P | 8 | 16 | 4500 | 5400 | 32MB | 105 | $399 | 7700X | ||

| 4344P | 8 | 16 | 3800 | 5300 | 32MB | 65 | $329 | 7700 | ||

| 4244P | 6 | 12 | 3800 | 5100 | 32MB | 65 | $229 | 7600 | ||

| 4124P | 4 | 8 | 3800 | 5100 | 16MB | 65 | $149 | New | ||

Since these are all based on AMD’s consumer discrete CPUs, the underlying architecture in all of these chips is Zen 4 throughout. So despite being positioned below the EPYC 8004 Siena series, you won’t find any Zen 4c CPU cores here; everything is full-fat Zen 4 CCDs. Which means that while there are relatively few cores overall (for an EPYC processor), they are all high-performing cores, with nothing turboing lower than 5.1GHz.

Notably here, AMD is mixing in some of their 3D V-Cache chip SKUs as well, which are signified with the “PX” suffix. Based on the 7950X3D and 7900X3D respectively, both of these chips have 1 CCD with V-Cache stacked on top of them, affording the chip a total of 128MB of L3 cache. The remaining 6 SKUs all get the “P” suffix – indicating they’re 1 socket processors – and come with TDPs ranging from 65 Watts to 170 Watts.

This does mean that, by EPYC server standards, the 4004 series is not particularly energy efficient. This is a lineup that is intended to be cost-effective first and foremost. Instead, energy efficiency remains the domain of the EPYC 8004, with its modestly-clocked many-core Zen4c designs.

The reuse of Zen 4/AM5 means that the EPYC 4004 series comes with all of the features we’ve come to expect from the platform, including 28 lanes of PCIe 5.0, 2 channels (128-bits) of DDR5 memory at speeds up to DDR5-5200, and even integrated graphics. Since this is a server part, ECC is officially supported on the chips – though do note that like the Ryzen Pro workstation chips, this is UDIMM-only; registered DIMMs (RDIMMs) are not supported.

AMD isn’t disclosing the chipset being paired with the EPYC 4004 processors, and while it’s undoubtedly going to be AMD’s favorite ASMedia-designed I/O chipset, it’s interesting to note that it’s at the motherboard level where the new EPYC platform’s real server credentials are at. Separating itself from rank-and-file Ryzens, the EPYC 4004 platform is getting several additional enterprise features, including baseboard management controller (BMC) support, software RAID (RAIDXpert2 for Server), and official server OS support. To be sure, this is still a fraction of the features found in a high-end enterprise solution like the EPYC 9004/8004 series, but it’s some additional functionality befitting of a platform meant to be used in servers.

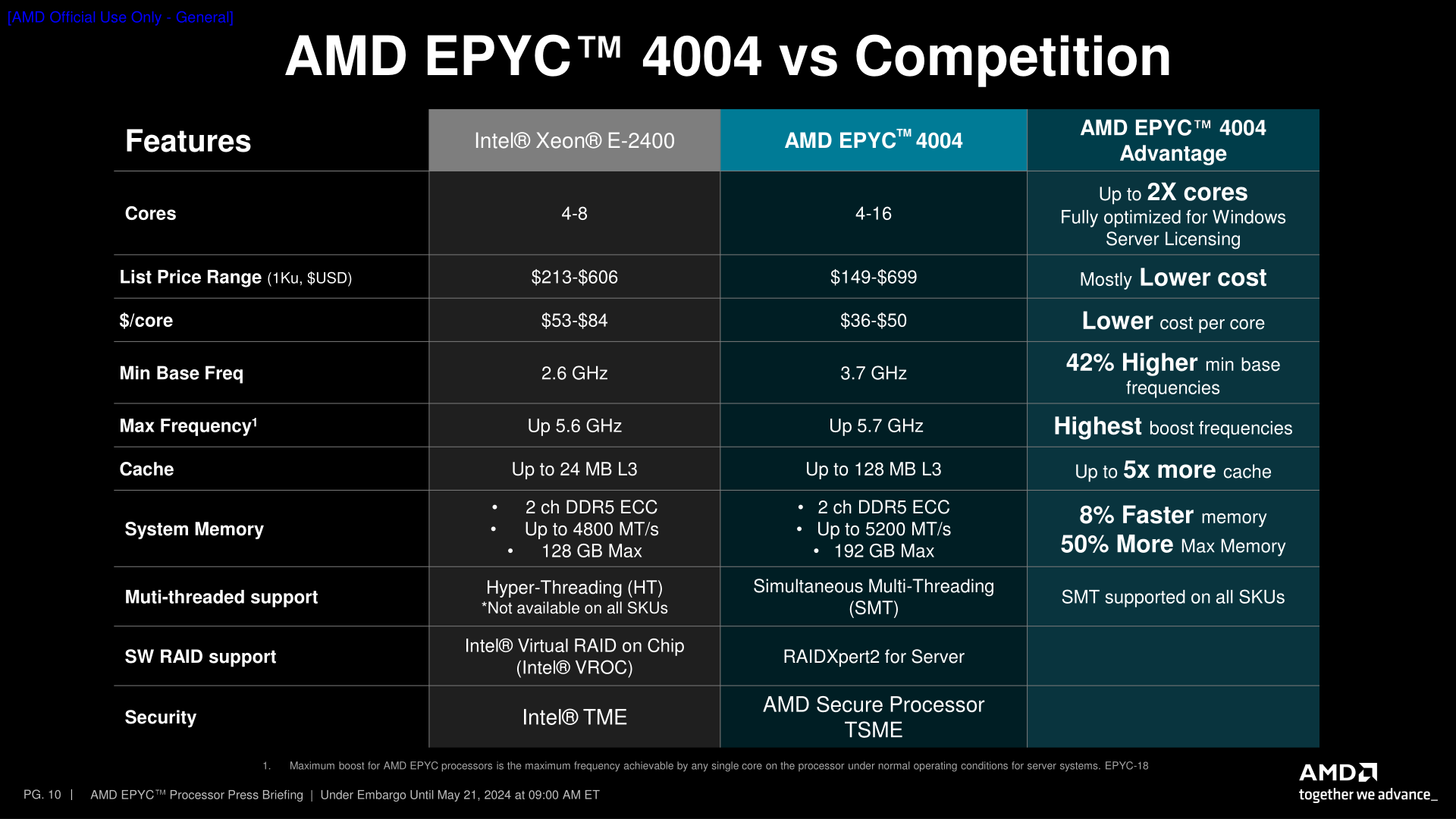

AMD’s new chips, in turn, are designed to compete against Intel’s entry-level Xeon-E family. Itself a redress of consumer hardware (Raptor Lake), the Xeon-E family is a P-core only chip lineup, with Intel offering SKUs with 4, 6, or 8 CPU cores. This leaves the EPYC 4004 family somewhat uniquely positioned compared to the Xeon-E family, as Intel doesn’t have anything that’s a true counterpart to AMD’s 12 and 16 core chips; after Xeon-E comes the far more capable (and expensive) Xeon-w family. So part of AMD’s strategy with the EPYC 4004 family is to serve a niche that Intel does not.

(As a side bonus, AMD’s core counts also end up playing well with Windows Server 2022 licensing. The Standard license covers up to 16 cores, so a top-end EPYC 4004 chip lets server owners max out their license, amortizing the software cost over more cores)

With regards to performance, Raptor Lake versus Zen 4 is largely settled by now. So I won’t spend too much time on AMD’s (many) benchmark slides. But suffice it to say, with a significant core count advantage, AMD can deliver an equally significant performance advantage in highly multi-threaded workloads (though in that scenario, it does come with a similar spike in power consumption compared to the 95 Watt Intel chips).

Wrapping things up, AMD is launching the new EPYC 4004 product stack immediately. With many of AMD’s regular server partners already signed up – and the core hardware readily available – there won’t be much of a ramp-up period to speak of.

Source: AMD

14 Comments

View All Comments

Terry_Craig - Tuesday, May 21, 2024 - link

I don't understand the logic of this product... I could just use the 7950X instead...shing3232 - Tuesday, May 21, 2024 - link

For enterprise userThreska - Tuesday, May 21, 2024 - link

Price mainly. EPYC even on the low-end as been pricey, hence the Ryzens.questionlp - Tuesday, May 21, 2024 - link

Two key reasons: official BMC support and official server OS support. Even if it's not for a typical Enterprise customer, there are smaller shops that need to run specialized software that will only certify server hardware (see VMware, Oracle, etc.).The difference here is that Intel's entry level Xeons lose out on their E cores due to VMware doesn't support hybrid chip configurations and end up being worse deals for those that need basic but certified hardware.

PeachNCream - Tuesday, May 21, 2024 - link

Epyc also has no E cores.pthariensflame - Tuesday, May 21, 2024 - link

Yes? AMD doesn't make any E-cores. (And if you'd dispute that and call Zen 4c an "E-core", then EPYC *does* have them, in Bergamo and Siena.)alpha754293 - Wednesday, May 22, 2024 - link

Watch the video from Patrick Kennedy from ServeTheHome. https://www.youtube.com/watch?v=JokLRV6KLeEHe answers this question explicitly.

Kevin G - Tuesday, May 21, 2024 - link

I was hoping for a model with 192 MB of aggregate of L3 cache with these models. The dual CCD but only one with 3D V-cache is an odd configuration. There is a case for a 'best of both worlds' philosophy here between cache and clock speeds but tuning where applications run for best performance is necessary (core parking etc.). A slightly lower clocked, 16 core, 192 MB of L3 cache model would provide some simplification for deployments.While unlikely but would've been nice is to have is the single CCD models (those 8 cores and below) have a new interposer that leverages two Infinity Fabric links to the CCD. The Zen 4 CCD designs support dual links to the IO die but AMD has not deployed any models actually leveraging this which would provide a nice bandwidth boost. This would give these chips an edge for some workloads vs. their earlier consumer counterparts.

cp0x - Sunday, May 26, 2024 - link

They definitely needed to include the 7800x3d equiv if they didn't pull off the trick you're suggesting ...FWhitTrampoline - Tuesday, May 21, 2024 - link

"Since these are all based on AMD’s consumer discrete CPUs, the underlying architecture in all of these chips is Zen 4 throughout."The CCDs for All Epyc/Ryzen generational products come from the same CCD diffusion lines and are just binned for performance metrics, and so the cream of the crop CCD samples goes into Epyc/TR Pro while Ryzen gets the leakier CCDs that may require more voltage to operate stably! To my understanding most of the I/O differentiation between Epyc/Ryzen happens at the I/O die level with only minimal CCD features disabled.

Does each Epyc bound CCD get 2 Infinity fabric links per CCD enabled to the I/O Die whereas for Ryzen only one of the 2 IF Links to the I/O die per CCD is enabled? And there is no RDIMM supported on these SKUs?

And as far as the V-cache do the Epyc parts not have options for both CCDs to have V-Cache stacked on top? Is the I/O die utilized here not having some extra features enabled that is not for any consumer variant if there's some extra IP that's not mentioned by AMD but is there for special use cases?