Intel Joins CHIPS Alliance, Contributes Advanced Interface Bus

by Anton Shilov on January 24, 2020 11:00 AM EST

Intel this week became a member of CHIPS Alliance, an industry consortium that is working to accelerate the development of open source SoCs (and SiPs) for various applications. As part of their membership, Intel has also contributed its Advanced Interface Bus to the group, giving developers access to the bus and thus the means to interoperate with Intel (and other) chips that will be using it.

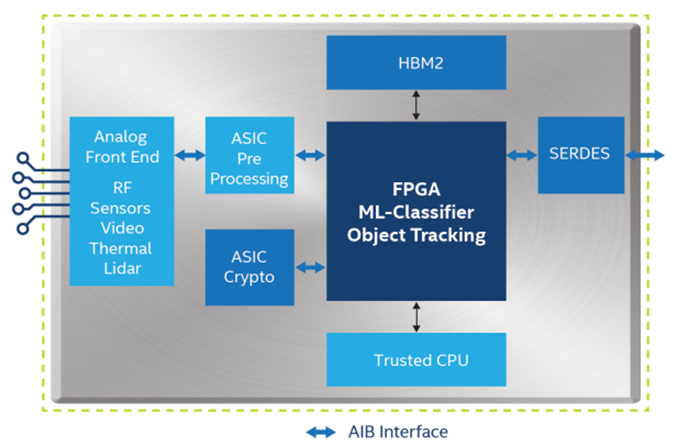

Designed for use with system-in-packages (SiPs) devices, Intel’s AIB is a high-bandwidth, low-power, die-to-die PHY level standard that uses a clock forwarded parallel data transfer mechanism (akin that used by modern DDR DRAM interfaces). The technology is agnostic to manufacturing processes and packaging technology, so it can be used to connect a wide variety of chips/chiplets using different types of packages, including Intel’s own EMIB, TSMC’s CoWoS, or other 2.5D technologies from numerous vendors.

Intel’s AIB has been available to third parties on a royalty-free basis for a while now, so contributing the technology to CHIPS Alliance is the next step for Intel in increasing its adoption. By making AIB available to a very broad group of chip designers, Intel is encouraging development of an ecosystem of chiplets that can later be used with its own CPUs, GPUs, FPGAs, and other components to build special-purpose multi-die SiPs.

Now that CHIPS Alliance controls Advanced Interface Bus specification, further development of the technology will be handled by its Interconnects workgroup, which is set to begin its operations shortly. As a part of the consortium, Intel will be able to further contribute to development of AIB. Meanwhile, Intel will get a seat on the governing board of CHIPS Alliance.

Dr. Zvonimir Bandić, Chairman, CHIPS Alliance, and senior director of next-generation platforms architecture at Western Digital said the following:

“Intel’s selection of CHIPS Alliance for the AIB specifications affirms the leading role that the organization impacts for open source hardware and software development tools. We look forward to faster adoption of AIB as an open source chiplet interface.”

Related Reading:

- Intel Provides Royalty-Free License for Data Bus to DARPA’s Modular Chips Initiative

- An Interconnected Interview with Intel’s Ramune Nagisetty: A Future with Foveros

- Intel’s Xe for HPC: Ponte Vecchio with Chiplets, EMIB, and Foveros on 7nm, Coming 2021

- Intel’s EMIB Now Between Two High TDP Die: The New Stratix 10 GX 10M FPGA

- Arm Joins CXL Consortium

- AMD Joins CXL Consortium: Playing in All The Interconnects

- Compute Express Link (CXL): From Nine Members to Thirty Three

- CXL Specification 1.0 Released: New Industry High-Speed Interconnect From Intel

- Gen-Z Interconnect Core Specification 1.0 Published

Source: CHIPS Alliance

17 Comments

View All Comments

CajunArson - Friday, January 24, 2020 - link

Not only is Intel inside CHiP's, they even release a slick promo video showing how they can merge onto the superhighway of connectivity!https://www.youtube.com/watch?v=D5-bD372v5s

HStewart - Friday, January 24, 2020 - link

Very funny, at least it was not horrible remake movie.edzieba - Friday, January 24, 2020 - link

I was sure they did this almost two years ago: https://fuse.wikichip.org/news/1520/intel-opens-ai... ? Unless the DARPA CHIPS program and the CHIPS Alliance are two identically named entities with the same function but not actually the same thing.CharonPDX - Friday, January 24, 2020 - link

They are indeed very similar, with identical names - but are completely different programs.DARPA CHIPS: Common Heterogeneous Integration and IP Reuse

CHIPS Alliance: Common Hardware for Interfaces, Processors and Systems

Similar goals, different organizations.

Hulk - Friday, January 24, 2020 - link

Please forgive my unfamiliarity with this topic...What devices would we see the benefits of this technology and what would the real world benefits be?

HStewart - Friday, January 24, 2020 - link

I think the main benefits are that chips with different technology can combine together in a chiplet that small and extremely fast - this can most be shown in i8705g which combines a Intel CPU with AMD designed GPU along with 4G of high speed memory. This can be found in laptops like the Dell XPS 15 2in1name99 - Friday, January 24, 2020 - link

The question is, are we going to see much of this:(a) connecting together chiplets from DIFFERENT vendors (so that standards are necessary) AND

(b) for the purposes of devices that "you and I" care about (so no FPGAs and suchlike).

For (a) people assume something like the ARM ecosystem will arise. But I'm not sure how varied the ARM ecosystem TODAY is. It looks to me like people get one collection of IP from ARM (CPU, maybe GPU, maybe NPU) and the rest is their stuff. In other words there's not much "multi-party" co-ordination necessary. In the ARM space, are there really people getting logic from ARM, memory controller from somewhere else, USB controller from somewhere else, ..., so that there's actually 5 IP sources that need to be co-ordinated?

(And even if there, they all co-ordinate to what ARM says; no consortium necessary).

For (b) obviously the current chiplet champion is AMD. All internally sourced. One day, supposedly, Lakefield and Foveros will ship, but again all internally sourced. At some point presumably Apple will ship chiplets -- maybe for their desktop ARM, maybe for Apple RF on separate silicon from Apple SoC -- but again all internal.

It's easy to make up a story about how great mix-and-match chiplets will be. It's a little harder to connect that to reality once you consider what most people actually need and want from their computing. It's always nicer to put everything on a single SoC, and it's hard to come up with cases of separate chiplets that correspond to independently developed IP.

Your Intel example is cute, but of course those were CHIPS, not CHIPLETS, that were packaged together. Will it happen again at the chiplet level?

Part of me thinks that something like PCIe, while nice as a common standard, is also SLOW to develop, being a common standard... Will people stick with the spec from 3 years ago, especially if they don't need to because all their parts are internally sourced?

And then we get that the AMD chiplet won't talk to the Intel chiplet bcs Intel is using the spec from 3 yrs ago, AMD has moved on, and there seemed no reason for them, at design time, to stick with the spec.

mode_13h - Saturday, January 25, 2020 - link

Why (b)? You're basically excluding the whole embedded market, which I think is one of the main sectors they're targeting.While Apple has volumes & margins big enough to justify a monolithic die, a lot of embedded SoCs are more niche, and would find it more cost-effective to use pre-made chiplets to suit their needs.

rahvin - Friday, January 24, 2020 - link

Think of it like the ability to add co-processor to a CPU.Something like an AI chip that's got a hi-speed interface with the CPU allowing the CPU to offload compatible tasks to the AI chip without the huge latency that would normally happen.

HStewart - Friday, January 24, 2020 - link

the chip in my Dell XPS 15 2in1 had the CPU, Discrete AMD GPU and memory on it. But it could have an AI chip - it really does not matter and does not required the same process for each component.