Phison Readies PS2251-17: A USB 3.2 Gen 2x2 Controller for External SSDs

by Anton Shilov on June 19, 2019 11:00 AM EST- Posted in

- SSDs

- Storage

- Trade Shows

- Phison

- 3D NAND

- Computex 2019

- PS2251-17

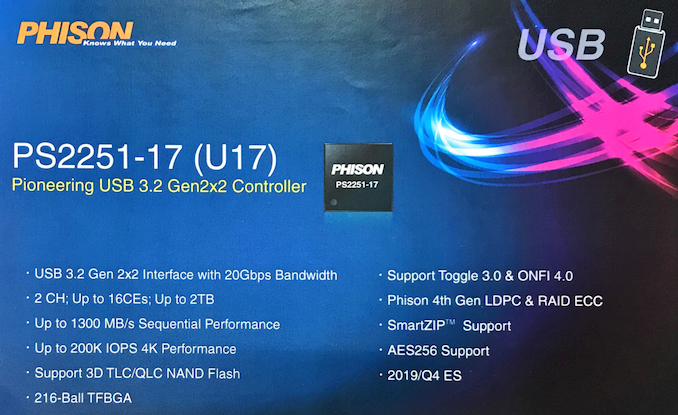

At this year's Computex trade show, Phison revealed that it is working on a USB 3.2 Gen 2x2 controller for external SSDs. Dubbed the PS2251-17 (U17), the company expects drives based on the chip to offer sequential transfer rates up to 1300 MB/s, which is notably higher than USB SSDs featuring a lower-bandwidth USB 3.2 Gen 2 interface. Retail USB drives based on this new controller, in turn, should be available sometime next year.

The Phison PS2251-17 controller features two NAND channels with 16 CEs that support modern types of flash, including 3D TLC and 3D QLC NAND, with Toggle 3.0 or ONFI 4.0 interfaces. The chip also supports Phison’s 4th Gen implementation of LDPC and RAID-based ECC, SmartZIP technology, AES256, and other features found on other controllers from this company.

When it comes to performance, Phison says that SSDs based on the PS2251-17 will offer up to 1300 MB/s sequential read/write speeds as well as up to 200K IOPS. Real-world performance will, of course, depend on type of 3D NAND use as well as implementation by the manufacturer.

Phison plans to sample single-chip controller for USB 3.2 Gen 2x2 solid-state storage devices in the fourth quarter of this year. Retail drives would then follow in later quarters, hitting the market sometime in 2020.

| Want to keep up to date with all of our Computex 2019 Coverage? | ||||||

Laptops |

Hardware |

Chips |

||||

| Follow AnandTech's breaking news here! | ||||||

8 Comments

View All Comments

TheUnhandledException - Wednesday, June 19, 2019 - link

usb 3.2 gen 2x2. No matter how many time I see it, it doesn't look any less stupid.sftech - Wednesday, June 19, 2019 - link

"usb 3.2 gen 2x2" could only be invented in a minimum of 10 meetings of 15 people or more. Is it the worst named standard ever? r/assholedesign at its bestChaitanya - Thursday, June 20, 2019 - link

They have decided those new names while high, as if the "branding" stupidity of USB 3.1 wasn't enough they went and decided on new 3.2 confusion.shabby - Thursday, June 20, 2019 - link

Don't worry they'll fix it with usb 4... Fingers crossedrepoman27 - Thursday, June 20, 2019 - link

I get that it's the cool thing to do to complain about USB nomenclature these days, but the only thing demonstrating stupidity here are your comments."Universal Serial Bus" is the name of the standard, which is often abbreviated by the initialism "USB".

"Universal Serial Bus 3.2 Specification" is the title of a specification, in the form of a pdf document, where "3.2" is the current release number.

This specification includes descriptions of two PHYs, one that was introduced in the 3.0 release of the spec and operates at 5 GT/s with 8b/10b encoding, and one that was introduced in release 3.1 and operates at 10 GT/s with 128b/132b encoding. Within the specification, these are referred to as "Gen 1" and "Gen 2".

The 3.2 release also describes channel bonding in the form of "dual-lane operation". Like every other I/O specification in history, it also adopts the convention of indicating the number of lanes in a link with a lower case "x" followed by the number of lanes.

None of this is different from any other specification out there, or involves branding, trademarks, or marketing in any way. Nor is any of it particularly confusing if you've learned to count to 2.

Contrast this with how you properly describe a PCI Express link, where you also have to indicate the signaling generation and lane width: "PCIe Gen3 x16". Why is "USB 3.2 Gen 2 x 2" so unpalatable? Is it the spaces after the "Gen" and the "x"? Or is it that you have to include both the specification release number and signaling generation for USB, whereas with PCIe you generally only need to include one of those, i.e. "PCIe 3.1a x16" or "PCIe Gen3 x16"? Is it because we continue to refer to every PCIe device with a Gen3 PHY as "PCIe 3.0" despite the fact that the PCI Express Base Specification Revision 3.1a was released back in December of 2015?

"USB" is the name of the standard, "3.2" is the version number of the specification, and "Gen 2 x 2" describes the signaling capabilities of this particular device, the Phison PS2251-17 (U17). And you're complaining about the USB-IF's choices here, not Phison's? Do you have a more convenient way of describing an interface with two PHYs and multiple link widths?

deathwombat - Thursday, June 20, 2019 - link

Well, yes.Everyone knows that each new version of the USB standard is a superset of the previous one, so it goes without saying that a USB 2.0 port supports both of the speeds that were introduced with USB 1.0 (Low speed and Full speed), and that 3.0 supports the speed that was introduced with 2.0 (High Speed), and that 3.1 supports the speed that was introduced with 3.0 (Super Speed), and that 3.2 supports the speed that was introduced with 3.1 (Super Speed+). There's no need to say "USB 3.1 Gen 1" when you mean Super Speed and "USB 3.1 Gen 2" when you mean Super Speed+: you can just say "USB 3.0" when you mean 5 Gbps and "USB 3.1" when you mean 10 Gbps. You know, like everyone is going to do anyway. The "Gen 1" and "Gen 2" stuff is just an extra thing to remember: "USB 3.1 Gen1" means "USB 3.0" speed. Likewise, no one cares that the 20 Gbps speed is achieved by combining two Gen 2 lanes. That's irrelevant to me! Just call it "USB 3.2". Everyone is going to, anyway, and you're just confusing them when you try to convince them to do otherwise. Lots of people aren't going to know what "Gen 1" and "Gen 2" mean, and they really aren't going to know what "Gen 2x2" means. Was there a compelling reason not to call it "Gen 3" to make it slightly more obvious that Gen 1 = 3.0, Gen 2 = 3.1, and Gen 3 = 3.2? I mean, lose the Gen stuff, but if you're going to keep it, at least be consistent!

Also, your comparison to PCIe makes no sense. It's "PCIe Gen3 x16". It's not "PCIe 3.2 Gen3 x16". The format is "[Standard] [version] [lane count]". For USB 3.2, it's "[Standard] [version] [generation] [lane count]". You just talked about people learning to count to 2, but you apparently can't count to 4! The PCIe naming standard tells you just what you need to know: generation (speed per lane) and the number of lanes, which you can multiply to derive bandwidth. Everyone understands that PCIe 3 is backwards compatible with PCIe 1 and 2 cards, so they don't clutter the name with "PCIe 3 Gen1" when they talk about PCIe 3 running at PCIe 1 speeds, or "PCIe 3 Gen2" when they talk about PCIe 3 running at PCIe 2 speeds. If I mean PCIe Gen2 speed, I say "PCIe 2", even when I'm putting the card in a PCIe 3 slot. I don't care to be more explicit than that because, you know, life is short, and excuse me for wanting to keep things simple so that I can focus on the things that I actually care about. Engineers and developers may need to care about how the underlying technology and how the speed is actually achieved, but consumers just want to know how fast the thing is without having to ask Google.

FreckledTrout - Thursday, June 20, 2019 - link

LOL It bothers be as well. Why they chose to segregate USB using such lengthy names baffles me. Just make everything to the USB 3.2 2x2 standard not the regular 3.2 10Gbps variant and call it USB 4. Thats it really nothing else needed.1_rick - Thursday, June 20, 2019 - link

These people need a John Sheppard: "it's official: you don't get to name anything. EVER."