The Samsung Galaxy S20+, S20 Ultra Exynos & Snapdragon Review: Megalomania Devices

by Andrei Frumusanu on April 3, 2020 9:30 AM ESTThe Exynos 990 SoC: Last of Custom CPUs

While we've received a lot of information on the Snapdragon 865 over the last few months due to Qualcomm’s openness and willingness to share details with the public, until now we’ve known almost nothing about the new Exynos 990. Samsung LSI’s newest flagship processors was announced way back in October, but we had to be patient and await commercial devices before we could get any concrete details on the chip’s makings. What we do know is that the new chip employs a new generation M5 CPU microarchitecture, upgrades the mid-cores to Cortex-A76 designs, and employs a new Mali-G77 GPU, all manufactured on a 7nm 7LPP process that uses EUV lithography.

An Exynos 9820 Retrospective

Before we get into the Exynos 990 itself, I want to do a quick retrospective on last's year's flagship Samsung SoC, the Exynos 9820, both to catch up on things we've learned since the Galaxy S10 launch, and to illustrate how the Exynos 990 has changed things.

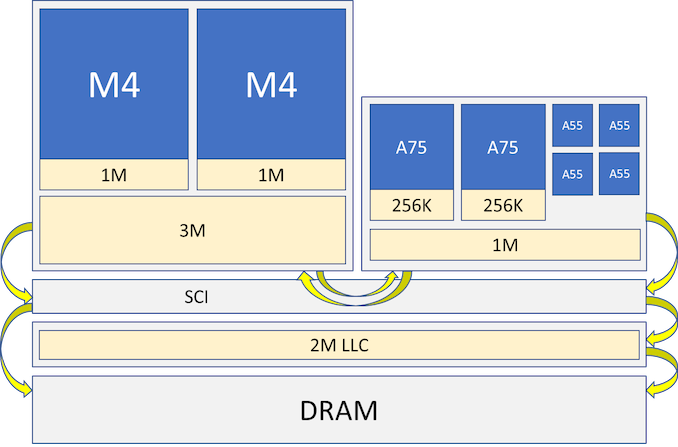

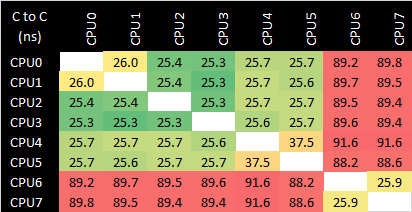

The first thing to note on the Exynos 9820 is that Samsung’s custom CPU cores reside in a completely different cluster than Arm’s cores – both being interconnected and being cache coherent only via Samsung’s Coherent Interconnect. My more recently written core-to-core latency test demonstrates this topology difference as the latencies between CPUs on the different cores is significantly higher than what we see on the cores within the Arm cluster, and higher than what we saw on the Snapdragon 865 on the previous page.

The second correction is that the M4 cores didn’t just have 512KB L2 caches, but rather 1MB. This wasn’t very visible in the latency tests due to issues with the microarchitecture which we’ll revisit in a later page as well.

The weird cache behavior that we originally reported on in the bandwidth figures of the A75 cores last year ended up being a side-effect of a 2MB last-level cache on the SoC. This SLC acts the same as the 3MB SLC on the Snapdragon 865 and allows for efficient caching of various memory accesses of the SoC IP blocks, saving power for the system.

Enter the Exynos 990

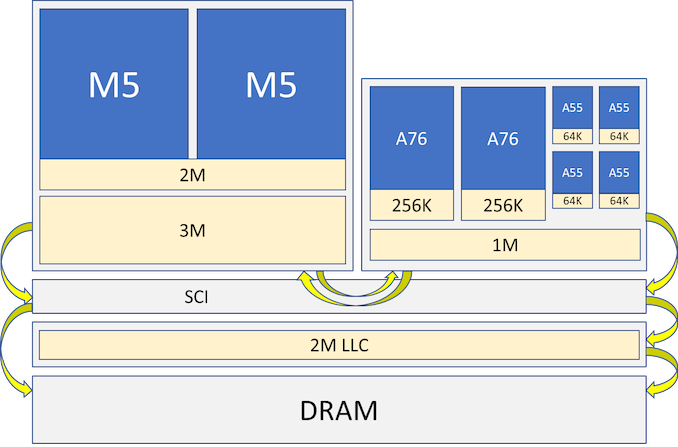

Where the Exynos 990 differs from the Exynos 9820 is in a few areas. First off, let’s focus on the Arm cluster. Here Samsung has finally donned the small A55 cores with private, 64KB L2 caches. This was notoriously missing from both the Exynos 9810 and Exynos 9820’s A55 cores, which lead them to be less performant and seemingly less efficient than their counterparts on the Snapdragon SoCs. The 64KB L2 caches here are still only half of the 128KB that we find on the Snapdragon 865, so Samsung continues to be extremely conservative in the cache configuration of the Arm CPUs. The new small cores see a slight clock frequency upgrade, going up to 2GHz this time around.

The middle cores see an upgrade from Arm Cortex-A75s to Cortex-A76s, while also getting a frequency lift from 2.3GHz up to 2.5GHz. This is actually a massive performance boost of 38% to 50% depending on the workload, and essentially serve as the Exynos 990’s workhorses for the vast majority of tasks. The L2 caches are still configured at 256KB per core, and the shared L3 of the Arm cluster remains at a more conservative 1MB.

On the big core side, we see the evolution of the microarchitecture from the M4 cores, codenamed Cheetah, to the newer M5 cores, codenamed Lion. Whilst Samsung has kept the maximum clock frequencies unchanged at 2.73GHz, they did promise a 20% uplift, which should mostly come from IPC improvements.

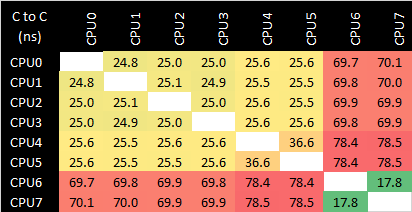

The biggest externally observable change is the fact that these new cores no longer have private L2 caches for themselves, but rather now come with a shared L2 of 2MB. That’s actually quite the huge microarchitectural design change in an era where we’re used designs actually introducing private L2 caches. The topology change can be evidenced by the drastic reduction in the core-to-core latencies between the two M5 cores compared to the M4 counterparts in the previous generation, as the coherency now happens at a lower cache level that's closer to the CPUs.

The Exynos 990 is manufactured on Samsung’s 7LPP node, which uses EUV lithography. It’s actually not the first chip on the process, as that title goes to the Exynos 9825 found in the Note10 series last year. However if TechInsight’s reporting is accurate, it seems that the that the Exynos 990 is the first chip to be actually designed with the full 7LPP PDK rather than being just a relaxed conversion of the design to another process (The 9825 is functionally identical to the 9820, and it seems this also applies to its lithography implementation).

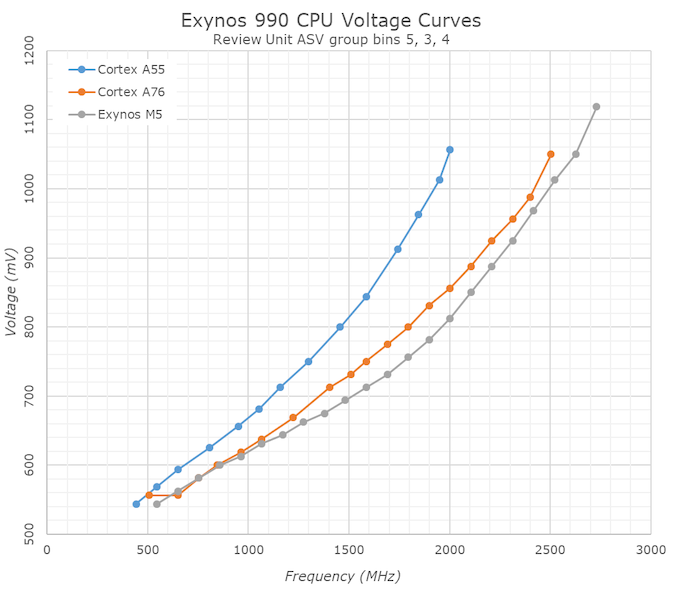

Samsung describes the 7LPP process as having 7% higher performance than its 8LPP node, which should also manifest itself as a power reduction of a design at otherwise equal frequency. Comparing the voltage curves of one of our S20 Exynos 990 units to the S10 unit last year, we see that there are some differences, but these are somewhat lackluster in the end. First of all it’s to be noted that the bins of our Exynos 990 units are seemingly bad this year, and I’ve seen that most units out there are in the same classification or even worse, pointing to the possibility of bad yields for the chip.

The A55 cores do clock slightly higher this generation, but at the peak frequencies the voltages still remain very high. At more medium frequencies we do however see improvements of up to around -43mV. The A76 cores can’t really be compared to the A75 cores of the previous generation due to their different microarchitectures, but also here we see the voltage curves being lower than on the 9820 even though the binning of our 990 units here are quite worse.

Finally, the M5’s core voltages are extremely disappointing. Not only are there no improvements at equal frequency to the M4 cores on 8nm, but there’s actually a degradation in the frequency scaling: the new Lion cores require higher voltages to reach the same frequencies. Peak voltages at 2.73GHz have gone up from 1068mV to 1118mV in our review sample units between the M4 and M5, meaning the new microarchitecture just scales worse in frequency. This all doesn’t bode all to well for power efficiency of the new design.

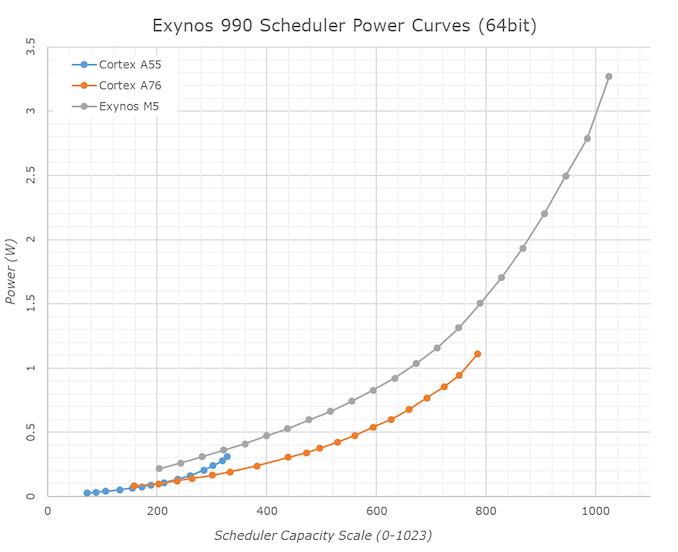

Samsung’s own scheduler and CPU characterization is very clear on the power and efficiency curves: throughout its performance scaling, the M5 cores are notably less efficient than the Cortex-A76 cores on the same SoC. We also note that the A55 data this year seemingly looks more realistic than what we’ve encountered on the Exynos 9820’s drivers last year.

The most striking differences in the power data from Samsung is the static leakage characteristics of the A76 and M5 cores. At an equal 1050mV voltage (2.5GHz on the A76, 2.6GHz on the M5), the Arm cores are characterized as leaking 78mW statically while the M5 cores use up 297mW. Static leakage is roughly corresponding to die area of the block – last year’s M4 cores were 3.72x larger than the A75 cores, and the static leakage difference here on the Exynos 990 is 3.8x, and I wouldn’t be surprised if this also ends up being the difference in area between the two CPU types.

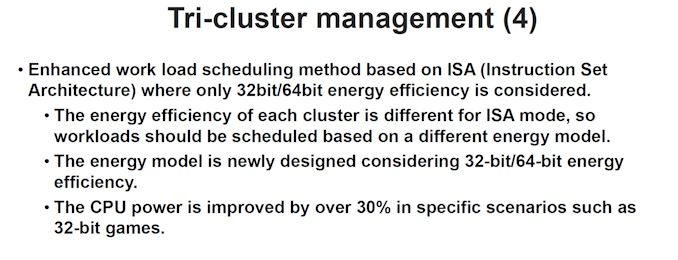

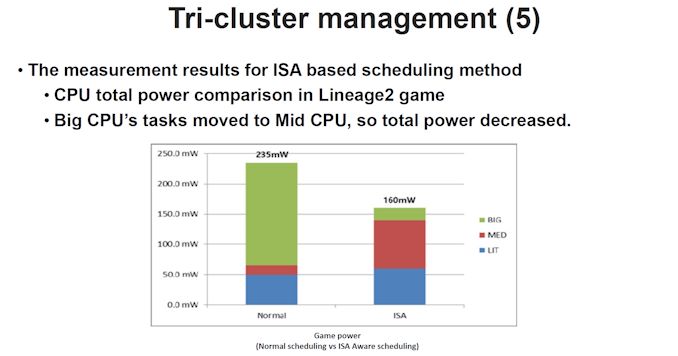

One odd mechanism that Samsung had introduced in the Exynos 9820 was a more complex scheduler that differentiated power models based on the running ISA of the application. It tracked 32 and 64-bit apps separately and made scheduler decisions based on the microarchitectural performance and power characteristics of the different CPUs on the different execution modes.

This is said to help power efficiency, mostly by scheduling things more often onto the Arm middle cores which seemingly have a better 32-bit execution efficiency.

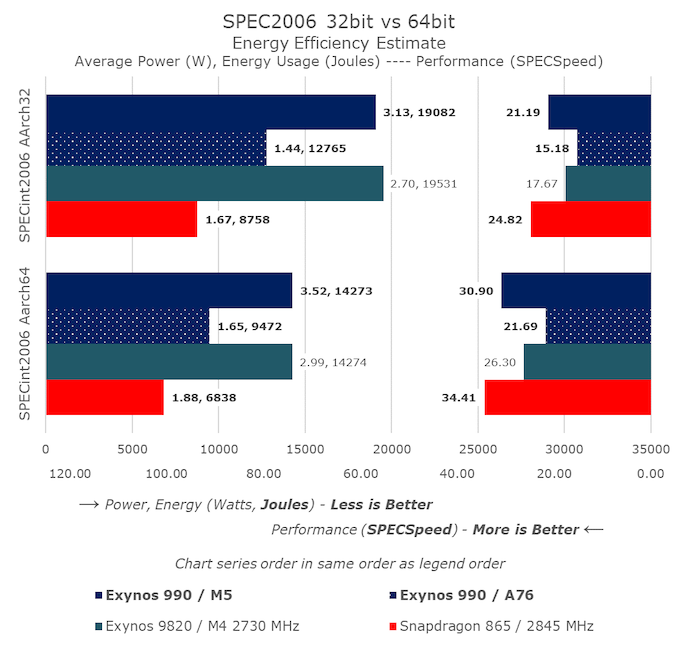

I was curious and I tried this out on the Exynos 990, comparing the relative differences in performance and efficiency between the M5 cores and the A76 cores. In the aggregate figures of SPECint2006, I unfortunately didn’t see any big difference at all in the execution modes. However individual subtests such as 456.hmmer, which are mostly execution bound, saw large advantages on the A76 cores, actually outperforming the M5 cores with a score of 13.53 vs 12.83 while using only half the energy. So in that regard, Samsung’s scheduling methodology makes a lot of sense. 400.perbench was another case of the A76 cores outperforming the M5 cores in 32-bit mode, using less than half the power. However, any more memory intensive workloads heavily favored the M5 cores, probably due to the stark differences in cache sizes. While I’m sure Samsung’s ISA based scheduling model reduces power, I do have to wonder what the absolute performance impact is in terms of using this mechanism.

Also unrelated to the whole ISA scheduling mechanism, I think this is the first time we’ve ever published benchmark numbers on the differences between AArch32 and AArch64 execution modes. The AArch64 performs significantly better due to it having more architectural registers available and being able to execute out-of-order code more efficiently, along with some ISA instruction improvements. Whilst there’s a power increase in this mode, we’re seeing much better efficiency as the performance improvements are greater. It’s also a good reason as to why the wider ecosystem is shifting to deprecate 32-bit on Arm.

It’s also to be noted that the M5 Lion core will be Samsung’s last commercial custom CPU design, as the design team had been disbanded back in October, and most employees by now have found new homes at different companies. I’ll be coming back to this decision in the context of the wider competitive landscape after we dissect the M5’s performance and efficiency.

137 Comments

View All Comments

Shadowfax_25 - Friday, April 3, 2020 - link

Excellent article, Andrei. The team over at XDA Developers managed to identify the adb commands which would allow you to set the display to either of the other refresh rates, so I'm sure Samsung could in some way introduce variable refresh rate switching.Here's the article for your perusal: https://www.xda-developers.com/samsung-galaxy-s20-...

Andrei Frumusanu - Friday, April 3, 2020 - link

Yea I saw that. In an ideal case Samsung would actually implement their own pseudo-VRR mode that switches between the display refresh rates based on content.Shadowfax_25 - Friday, April 3, 2020 - link

One more thing: it appears as if the commentary around the speaker evaluation is missing.Shadowfax_25 - Friday, April 3, 2020 - link

Ignore, looks like it was a caching issue on my side.eastcoast_pete - Friday, April 3, 2020 - link

Yes, but that would make sense, and this is Samsung we're talking about here. Still, there's hope, I guess.CecilFitzgerald - Monday, October 12, 2020 - link

Machine learning is in great need now. During the coronavirus period, it would be nice to identify some dependencies and foresee what will happen next in the world. By the way, if you also need to write an essay on machine learning, then i advise you to turn to https://buypapercheap.net/affordable-term-papers-f... which offers writing term papers at affordable prices.yeeeeman - Friday, April 3, 2020 - link

Andrei, amazing review TBH. You have outdone yourself once again and, fie vorba intre noi, cred ca esti succesorul cel mai potrivit pentru Anand. Esti cel mai profi si cand vine vorba de detalii tehnice, dar si de idei interesante de comparatie intre diferite device-uri. Am scris in romana sa nu se supere colegii tai.Please try to add to the energy efficiency table, Ice Lake scores and maybe some energy usages like you have for mobile devices? That would be amazing!

Unashamed_unoriginal_username_x86 - Friday, April 3, 2020 - link

avem traducere Google, tipuleyeeeeman - Friday, April 3, 2020 - link

Tipule, era o glumita. Logic ca poti folosi traducerea.abufrejoval - Saturday, April 4, 2020 - link

Born German with Latin as my first foreign language, and with fluent Spanish and French picked up later, written down Romanian isn't nearly as hard to understand as the spoken language... bine, bine!