Who Controls the User Experience? AMD’s Carrizo Thoroughly Tested

by Ian Cutress on February 4, 2016 8:00 AM ESTAMD’s Industry Problem

A significant number of small form factor and portable devices have been sold since the start of the century - this includes smartphones, tablets, laptops, mini-PCs and custom embedded designs. Each of these markets is separated by numerous facets: price, performance, mobility, industrial design, application, power consumption, battery life, style, marketing and regional influences. At the heart of all these applications is the CPU that takes input, performs logic, and provides output dependent on both the nature of the device and the interactions made. Both the markets for the devices, and the effort placed into manufacturing the processors, is large and complicated. As a result we have several multi-national and worldwide companies hiring hundreds or thousands of engineers and investing billions of dollars each year into processor development, design, fabrication and implementation. These companies, either by developing their own intellectual property (IP) or licensing then modifying other IP, aim to make their own unique products with elements that differentiate them from everyone else. The goal is to then distribute and sell, so their products end up in billions of devices worldwide.

The market for these devices is several hundreds of billions of dollars every year, and thus to say competition is fierce is somewhat of an understatement. There are several layers between designing a processor and the final product, namely marketing the processor, integrating a relationship with an original equipment manufacturer (OEM) to create a platform in which the processor is applicable, finding an entity that will sell the platform under their name, and then having the resources (distribution, marketing) to the end of the chain in order to get the devices into the hands of the end user (or enterprise client). This level of chain complexity is not unique to the technology industry and is a fairly well established route for many industries, although some take a more direct approach and keep each stage in house, designing the IP and device before distribution (Samsung smartphones) or handling distribution internally (Tesla motors).

In all the industries that use semiconductors however, the fate of the processor, especially in terms of perception and integration, is often a result of what happens at the end of the line. If a user, in this case either an end user or a corporate client investing millions into a platform, tries multiple products with the same processor but has a bad experience, they will typically relate the negativity and ultimately their purchase decision towards both the device manufacturer and the manufacturer of the processor. Thus it tends to be in the best interest of all parties concerned that they develop devices suitable for the end user in question and avoid negative feedback in order to develop market share, recoup investment in research and design, and then generate a profit for the company, the shareholders, and potential future platforms. Unfortunately, with many industries suffering a race-to-the-bottom, cheap designs often win due to budgetary constraints, which then provides a bad user experience, giving a negative feedback loop until the technology moves from ‘bearable’ to ‘suitable’.

Enter Carrizo

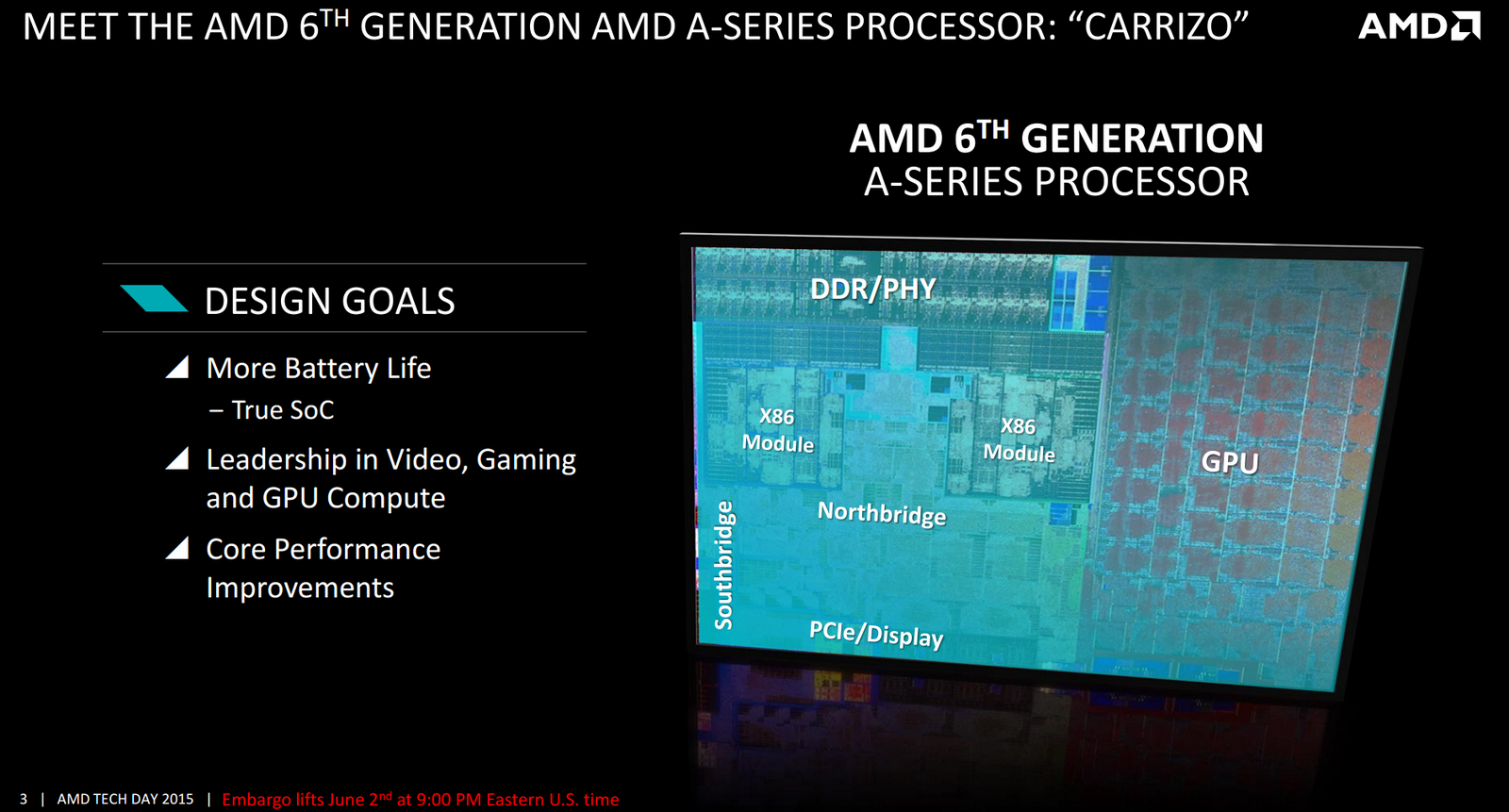

One such platform that was released in 2015 is that of AMDs Carrizo APU (accelerated processor unit). The Carrizo design is the fourth generation of the Bulldozer architecture, originally released in 2011. The base design of the microarchitecture is different to the classical design of a processor - at a high level, rather than one core having one logic pipeline sharing one scheduler, one integer calculation port and one floating point calculation port resulting in one thread per core, we get a compute module with two logic pipelines sharing two schedulers, two integer calculation ports and only one floating point pipeline for two threads per module (although the concept of a module has been migrated to that of a dual core segment). With the idea that the floating point pipeline is being used infrequently in modern software and compilers, sharing one between two aims to save die area, cost, and additional optimizations therein.

The deeper reasons for this design lie in typical operating system dynamics - the majority of logic operations involving non-mathematical interpretations are integer based, and thus an optimization of the classical core design can result in the resources and die area that would normally be used for a standard core design to be focused on other more critical operations. This is not new, as we have had IP blocks in both the desktop and mobile space that have shared silicon resources, such as video decode codecs sharing pipelines, or hybrid memory controllers covering two memory types, to save die area but enable both features in the market at once.

While interesting in the initial concept, the launch of Bulldozer was muted due to its single threaded performance compared to that of AMD’s previous generation product as well as AMD’s direct competitor, Intel, whose products could ultimately process a higher number of instructions per clock per thread. This was countered by AMD offering more cores for the same die area, improving multithreaded performance for high workload throughput, but other issues plagued the launch. AMD also ran at higher frequencies to narrow the performance deficit, and at higher frequencies, the voltage required to maintain those frequencies related in a higher power consumption compared to the competition. This was a problem for AMD as Intel started to pull ahead on processor manufacturing technology taking advantage of lower operating voltages, especially in mobile devices.

Also, AMD had an issue with operating system support. Due to the shared resource module design of the processor, Microsoft Windows 7 (the latest at the time) had trouble distinguishing between modules and threads, often failing to allocate resources to the most suitable module at runtime. In some situations, it would cause two threads would run on a single core, with the other cores being idle. This latter issue was fixed via an optional update and in future versions of Microsoft Windows but still resulted in multiple modules being on 'active duty', affecting power consumption.

As a result, despite the innovative design, AMDs level of success was determined by the ecosystem, which was rather unforgiving in both the short and long term. The obvious example is in platforms where power consumption is directly related to battery life, and maintaining a level of performance required for those platforms is always a balance in managing battery concerns. Ultimately the price of the platform is also a consideration, and along with historical trends from AMD, in order to function this space as a viable alternative, AMD had to use aggressive pricing and adjust the platforms focus, potentially reducing profit margins, affecting future developments and shareholder return, and subsequently investment.

175 Comments

View All Comments

ImSpartacus - Friday, February 5, 2016 - link

Holy shit, I haven't seen that many pages in a long time. You don't see this much content very often. Gotta love dat chorizo.close - Friday, February 5, 2016 - link

ImSpartanus, they're just writing a comprehensive article. I'm sure they put in good work with all of them.ImSpartacus - Friday, February 5, 2016 - link

I think this article provides a pretty delicate and nuanced treatment of chorizo and its place in the market (both potential & actual). There's no doubt that the circumstances demanded it. This was not business as usual and I'm glad Anandtech recognized the need for that additional effort.We're fooling ourselves if we pretend that any journalistic entity puts the sane amount of effort into every project. We're talking about living, breathing humans, not robots.

fmcjw - Friday, February 5, 2016 - link

I found the language convoluted, verbose, and difficult to read, compared to, say, Anand's straightforward and logical writing:"Nonetheless, Intel’s product line is a sequence of parts that intersect each other, with low end models equipped with dual core Pentiums and Celerons, stretching into some i3 and i5 territory while still south of $1000. In this mix is Core M, Intel’s 4.5W premium dual core parts found in devices north of $600."

"south of/north of"... can't you just put in "below/above"? And all that "intersecting of parts", can't you just say from the Atom to Pentiums, Celerons, i3's, and i5's....

The whole thing reads like they're paying you to score a high word count. Lots of information to extract here, but it can be 3 pages shorter and take half as long to read.

Cellar Door - Friday, February 5, 2016 - link

That is why Anandtech has video adds on their main page - designed for people like you. Who simply lack reading comprehension past 8th grade and find it hard to understand. Just watch watch the video on how to loose weight that auto-plays on the side.Or... try Tom's Hardware - they cater to your demographic.

ImSpartacus - Friday, February 5, 2016 - link

There's no question that Anand had a powerful way of writing that was uniquely simple yet educated you nevertheless. And for a layman that reads this sort of stuff to learn new information, that's very attractive and I kinda miss it (along with Klug).However, I give Ian a pass because he at least attempted to use other brand of conveying his ideas. In certain sections he used special table-like fitting to separate "parallel" sections/stances so that the rader would be more apt to compare them. So there's at least some effort, though he surely could do better.

10basetom - Saturday, February 6, 2016 - link

fmcjw does have a point, but in all fairness it is much harder to explain techical stuff in layman terms than it is to be long-wordy. Carl Sagan was the master of it on TV, and Anand was excellent at it on paper.JMC2000 - Sunday, February 7, 2016 - link

I didn't find anything wrong with the language Ian used, as this is piece is still on a technical level, but can be understood by the layman that knows a bit more than just what the stickers on the outside tell.To me, the phrase "parts that intersect each other" lays out that there is a myriad of options where configurations overlap, where as saying "from the Atom to Pentiums, Celerons, i3s and i5s" indicates that there is a pricing structure that is related to general CPU performance, which there really isn't when it comes to low-end machines.

plonk420 - Monday, February 8, 2016 - link

"south of/north of" sounds better than "greater than/less than," which is more correct than "below/above"Sushisamurai - Thursday, February 11, 2016 - link

yeah, colorful language is nice. Dumbing down adjectives or descriptions can often construe the true message IMO. This way, it paints a more descriptive/colorful picture.Keep up the good work Ian.