Arm Unveils 2024 CPU Core Designs, Cortex X925, A725 and A520: Arm v9.2 Redefined For 3nm

by Gavin Bonshor on May 29, 2024 11:00 AM EST- Posted in

- CPUs

- Arm

- Smartphones

- Mobile

- SoCs

- Cortex

- 3nm

- Armv9.2

- Cortex-A520

- Cortex X925

- Cortex A725

Arm Cortex A520: Same 2023 Core Optimized For 3 nm

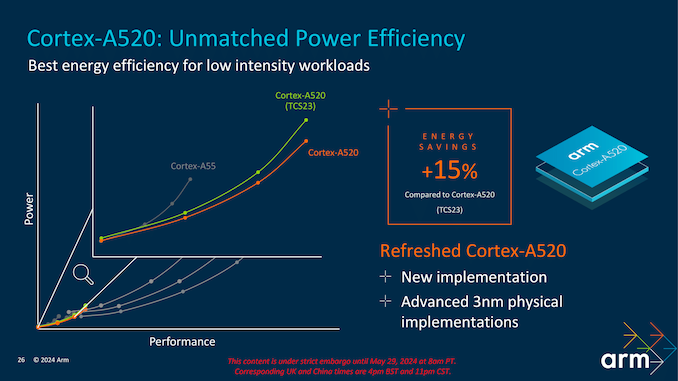

The Arm Cortex-A520 isn't architecturally different, nor has it been changed compared with last year's TCS2023 introduction. Instead, it has been optimized for the latest 3 nm process technology, enhancing its efficiency and performance. This core, part of the second-generation Armv9.2 architecture, delivers some additional compute power for everyday tasks in mobile and embedded devices while maintaining peak levels of energy efficiency and reducing power consumption expected from Arm's smallest core.

These architectural tweaks ensure that the Cortex-A520 can maximize the potential of the 3 nm process, achieving higher transistor density and better overall performance without any significant changes to its fundamental design.

The Cortex-A520 showcases a significant 15% energy saving compared to the Cortex-A520 (TCS23). This improvement is critical for devices with prolonged battery life, such as smartphones and Internet of Things (IoT) devices. By optimizing power consumption, the Cortex-A520 ensures efficient performance without compromising energy usage.

The graph on the above slide clearly illustrates the relationship between power and performance for the Cortex-A520 compared to its predecessor, the Cortex-A55, and the previous Cortex-A520 (TCS23). The latest Cortex-A520 explicitly designed for the 3 nm notably improves power efficiency across various performance levels. This means that the Cortex-A520 consumes significantly less power for a given performance point, demonstrating Arm's commitment to providing performance gains across 2024's Core Cluster and focusing on refining things from a power standpoint to the smallest of the three Cortex cores.

55 Comments

View All Comments

mode_13h - Thursday, May 30, 2024 - link

> Also, amazing increases in performance per watt doesn't mean less power draw.ARM provided power/performance curves, the point of which is to show how much more efficient the new cores can be at ISO performance, or how much more performance you can get at the same power, or what tradeoffs you can make anywhere in between.

I know their unitless graphs and lack of details about the workload used to produce them can stretch their credibility, but it's not as if they aren't aware that these cores often won't be clocked to the max. Reply

vegemeister - Friday, May 31, 2024 - link

In most client application, you always do 1x the work, and the only difference is how long it takes / what the CPU utilization % is.So the SoC will indeed use 1/1.33 as much energy. Reply

eastcoast_pete - Sunday, June 2, 2024 - link

It does overall if the OS and the SoC does "hurry up and get to idle" really well. This is something Apple's mobile SoCs have excelled at in recent times, it helps that their "Little" (efficiency) cores are strong performers that use out-of-order execution and other features to allow the SoC to stay on the efficiency cores for far longer. Android smartphones based on stock ARM cores don't have that option as much, and seem to end up running their larger cores more often and longer. Would also be interesting how much of that efficiency penalty can also be attributed to Android OS, but ARM has been very stubborn sticking to in-order execution for its Little cores. Which is puzzling, but good for Apple. Replymode_13h - Thursday, May 30, 2024 - link

I'm disappointed that ARM seems to have deviated from their practice of releasing ISO-power and ISO-performance figures.Also, I noticed they swapped the axis' in their power/performance graph so that it curves upwards rather than leveling off. I guess some marketing goon decided graphs look more impressive if they curve upward. And, as usual, we get the unitless graphs that don't start at zero.

Hey, does anyone know if the A520 still potentially shares vector FP units between a pair of cores, or did that gem of an idea begin and end with the A510? Reply

GeoffreyA - Thursday, May 30, 2024 - link

"shares vector FP units between a pair of cores"That was a Bulldozer principle, if I remember rightly. Reply

kkilobyte - Thursday, May 30, 2024 - link

Ok, sorry to remind you and maybe sound a little 'pushy' about it, but what about the i9-14900KS test redo with Intel Default settings? You told us 20 days ago that you'd redo them :Gavin Bonshor - Friday, May 10, 2024 - link

Don't worry; I will be testing Intel Default settings, too. I'm testing over the weekend and adding them in.

So, will this promise be ever fullfilled? Reply

mode_13h - Thursday, May 30, 2024 - link

+1Please deliver the promised update to the i9-14900KS review! The people deserve to know how much performance is being lost with Intel's new recommended defaults! Reply

watersb - Friday, May 31, 2024 - link

Pronunciation of their new software branding, 'Kleidi', is not completely clear to me.One way is to make it sound like the name of a girl, rhymes with 'Heidi'. So a single syllable.

The other way is to infer that the Arm Marketing people wished to evoke a colorful collection of myriad bits that can combine to form interesting patterns. A toy, A Kaleidoscope.

Unfortunately, that sounds like "Collide-y" to me: a product that tends to bang into other pieces.

Which would be an unfortunate name for automotive applications. Reply

EthiaW - Sunday, June 2, 2024 - link

ARM routinely claims the fruit of TSMC node improvement as its own achievement, you'll get familiar with the cliche after following it for a few years.🙄 As for competition, we are already seeing Apple 9-core M4, the 1.5 times bigger brother of A18. Halve the memory score and lower its frequency to a more phone-friendly 3.7Ghz, it's still scoring at least 3200 in geekbench single core which X925 is certainly not going to catch up with. By the time new ARM laptop hits the market Zen5 mobile and Lunar Lake will be prevalent and based on available data an single core improvement of at least 20% is expected so X925 will not have an easy time. I'd say this generation of ARM cores are mostly incremental and nothing revolutional. Replymode_13h - Sunday, June 2, 2024 - link

> ARM routinely claims the fruit of TSMC node improvement as its own achievement,There's nothing automatic about an IPC improvement. You have to actually make design changes to take advantage of the larger transistor budget and timing margins, in order to achieve that. Otherwise, the only way CPUs would get faster from shrinking nodes is just by increasing clockspeeds, which incurs a high cost in additional power.

Plus, how is this any different than what Intel and AMD do, when they announce new CPU microarchitectures? They don't usually separate out how much improvement is from the node, if ever.

> Zen5 mobile and Lunar Lake will be prevalent and based on available data

> an single core improvement of at least 20% is expected

At what power level? It's not 20% IPC, so there's some additional clockspeed in that figure, which might not be entirely applicable to laptops. Reply