Intel Unveils Meteor Lake Architecture: Intel 4 Heralds the Disaggregated Future of Mobile CPUs

by Gavin Bonshor on September 19, 2023 11:35 AM ESTI/O Tile: Extended and Scalable Depending on Segment

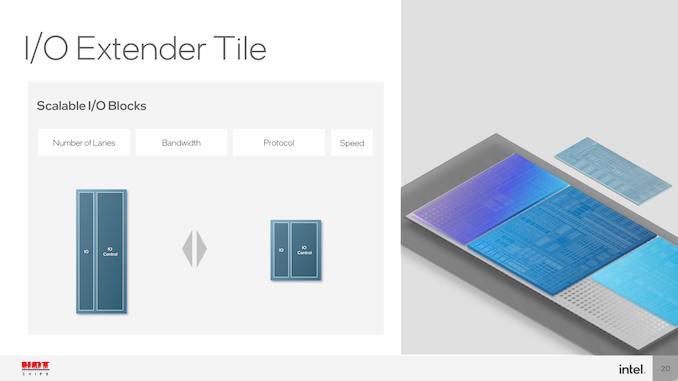

The smallest of Meteor Lake's tiles is the I/O tile, which is primarily designed to offer additional connectivity features. This, of course, is down to two things; specific vendor's needs and the grade of processor itself. As Meteor Lake is scalable, the I/O tile is perhaps the crux of enabling specific features such as Thunderbolt 4 on devices. A lower-end Intel Core 3 Meteor Lake chip is likely to drop flashy I/O-specific features such as TB4 to save on cost, as entry-level notebooks aren't going to use it.

The higher end of the Meteor Lake product stack will feature Thunderbolt 4, and although it will be on the I/O tile for notebook vendors to utilize, having a scalable I/O fabric allows Intel to implement a modular approach to I/O features instead of one that is more one size fits all. The I/O tile includes additional PCIe lanes, but this number will vary depending on the processor itself; a higher-end chip will have more for additional storage needs, whereas a lower-end chip will have the minimum for connectivity and whatnot. Something else is that the I/O tile isn't a PCIe Coherent Fabric, which means data can only be transferred without the support for cache coherency between memory and devices.

107 Comments

View All Comments

Eliadbu - Wednesday, September 20, 2023 - link

The adamantine cache is supposedly at the base tile that all other tiles are connected to.It wasn't mentioned here, maybe if it does exist on MTL we will see information about it when the CPUs will officially come out.

haplo602 - Thursday, September 21, 2023 - link

So now we will have 3 types of cores for the OS to schedule ... I hope Intel is working with OS vendors to properly implement this or it will be a nightmare ... we already saw the 12/13gen issues on Windows 10 and 11 with wrong E to P scheduling ....GeoffreyA - Thursday, September 21, 2023 - link

Complexity is good, says Intel.Vink - Friday, September 22, 2023 - link

Pat Gelsinger does a very good job and I'm speaking concretely because I use series 12 and 13 in the manufacture of Graphics Stations, Ultra PCs, and Standard PCs and they all work PERFECT with maximum benchmark and infinite Tau (only K series)... I'm looking forward to series 14 especially for its benchmark...JayNor - Friday, September 22, 2023 - link

" ...8 x Xe graphics cores with 128 vector engines (12 per Xe core) "16 per xe core

James5mith - Friday, September 29, 2023 - link

"This is because it's the first client processor to be made using chiplets instead of a monolithic design."Don't tell AMD.

dicobalt - Saturday, October 14, 2023 - link

Any indicators of future CAMM sockets integrated directly onto the CPU package?